# Design and Implementation of Interleaved Buck Converter in Network Communication for Femtocell Technology

Yashaswini H N M.Tech, Power Electronics Engineering, R V College of Engineering, India.

Dr. S.G.Srivani

Associate professor, Dept of EEE, R V College of Engineering, India.

Abstract - This paper describes about a design and implementation of Interleaved Buck Converter in network communication for Femto Technology. The evolution of wireless broadband technology improves the data speed rates and coverage and avoids the web surfing of the network which can be done by using Femtocells without the need of the expensive cell towers [1]. In the hardware architecture of the femto cell, the DC-DC converter such as Buck converter plays a important role which used to convert from the higher voltage to lower voltage towards the supply side of the femto cel. As this converter has the disadvantage of higher switching losses and increased inductor AC, reduction of efficiency, power density and power factor are also less[3]. In order to overcome from all these limitations, Interleaved buck converter has been introduced which has low switching losses & improves step down conversion ratio suitable for high input with the duty ratio of 0.4%.A closed loop control is achieved by designing a digital PID controller to achieve the proper regulator for this converter[4]. For the hardware implementation, power supply circuit, buffer driver circuit and Node MCU specifications has been analyzed to constant output voltage wrt flacutations present in the load. For the enhancement in updating the technology, this converter is connected to the GPRS IOT of ThingSpeak applications for the improvement in the network strength. The design and implementation of the closed loop control of the Interleaved buck converter with the input voltage of 12V and output voltage of 5V with the power rating of 10W for the Femto technology has been discussed[5]. In this proposed paper the hardware architecture of the femto cells along with the design and analysis of the closed loop Interleaved buck converter with the GPRS module has been validated.

Index Terms – Femtocells, Interleaved Buck Converter, PID controller, GPRS module, Power supply unit

## 1. INTRODUCTION

In cellular network communications, the high-speed coverage connection and generation of large traffic data of the network has been consumed by many services like web surfing, video streaming, email downloading, image downloading and video calls. The attenuations of the walls, multiple losses, scattering of the spectrum analysis are the primary problem for the poor cellular network communication [1]. The main challenge of the operators is to provide the good indoor coverage in cost effective manner with excellent network strength. The invent of the femtocells help to reduce the cell phone traffic which is soon riding on the consumers broadband line[2]. The poor coverage slows down the high speed data rates and reduces the quality of video and voice applications. But these cells has a disadvantage of high capital cost, leased backhaul connection, increases the electricity bills etc. Hence all these problem has lead to the solution of the cost effective technology which is a Femtocell[3].

A small box that plugs into the users existing broadband internet connections and works with the existing mobile networks is a Femtocell. These femto cells are fully featured, short range mobile phone base station has been evolved in order to avoid the existing problems like lack of indoor coverage and low data rates[4]. It is a low power base station with the low power range can be deployed in residence, office and enterprise applications. The main difference between the base station and femtocell is the radius of base station and femtocells are 20-30meter and 10 meter respectively[5]. The plug and play capability of the femtocells helps the user for the easy installation and usage. It provides excellent mobile coverage and data speed at home, office, and public areas for both voice and data.For 3G, 4G or Long term Evolution these Femto cells has been developed and approaching to NextGen i.e 5G by 2020 for better enhancement and data speed rates with multiple access[6].

There are many four types of small cells namely, the first one is Femtocells which is closed access with the 4 -8 users are operating within the radius of 10m[7]. The second one is Metrocells which is hybrid/open access with the 8 -32 users can be operated with the radius range of 200m. The third one is Pico or Micro cells which is a open access with the 32 -more than 100 users[8]. The fourth one is Macrocell which is a open access with more than 1000 users. The femtocell can be classified into three cells i.e Home cell, Enterprise cell and

## International Journal of Emerging Technologies in Engineering Research (IJETER) Volume 7, Issue 5, May (2019) www.ijeter.everscience.org

Metro cells[9]. It supports 4 users in a residential setting & 4 to 32 users in enterprise cell, 16 users in metro cells[10]. The different types of femtocell is as shown in the figure 1.2(a)(b)(c).

Fig 1.2(a): Front and back view of Femtocell

Fig 1.2(b): Different types of Metro Femtocell

Fig1.3: Various components of Femtocell

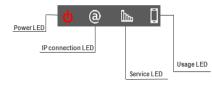

Fig1.4: Significance of LED of Femtocell

## 2. HARDWARE ARCHITECTURE OF FEMTOCELL TOWARDS SUPPLY SIDE

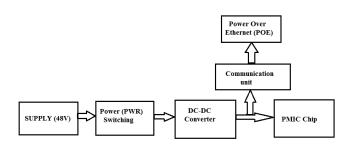

The components present in the hardware architecture of the femtocell are namely, DC -DC converter as Buck converter, PWR switching, Power Over Ethernet (POE) and PMIC chip which manages all the associated elements for the processing of the operations [1]. The block diagram of Femtocell towards supply side is as shown in Fig2.

Fig 2: Block Diagram of FEMTO cell towards supply side

- Supply: The primary function of a power supply is to convert electric current from a source of 48V for enterprise cell and 12V for home cell which delivers power to the load [2].

- Power (PWR) Switching: Power switching is a Switch Mode Power Supply (SMPS) is an electronic power supply that incorporates a switching regulator to convert electrical power more efficiently.

- DC-DC Converter: A DC-to-DC converter is an electronic circuit that converts a source of direct current (DC) from one voltage level to another. A buck converter (step-down converter) is a DC-to-DC power converter which steps down voltage from its input (supply) to its output (load). It has a input voltage of 12V converts into the output voltage of 5V efficiently which extends prolonged battery life, reduces heat dissipation.

- Power Over Ethernet (POE): Power over Ethernet or POE is a standard system which pass electric power along with data on twisted pair Ethernet cabling. This allows a single cable to provide both data connection and electric power to devices such as wireless access points like LAN port.

- PMIC: They are integrated circuits for managing power requirements of the system. It is often included in battery-operated devices such as mobile phones and portable media players to decrease the amount of space required. Power management ICs are solid state devices that control the flow and direction of electrical power[5]. It has a ability to perform some basic electrical functions including voltage conversion, voltage scaling, power source selection. It is equally suitable for DC-to-DC conversion on board without losing the bit of accuracy and quality of the signal. It is used for individual power conversion, where more than one function can be employed on the single IC based on the nature and quality of the product they are going to be installed. These Integrated chips help in reducing the number of components required to perform number of functions on a single chip[6].

## 3. METHODOLOGY OF INTERLEAVED BUCK CONVERTER FOR FEMTOCELL TECHNOLOGY

In the supply side of the Femtocell has a buck converter which converts from higher voltage of 12V to a lower voltage to 5V but this converter has a limitations of higher switching losses and reduces efficiency. In order to overcome from this limitations, the interleaved buck converter are introduced which provides a high efficiency, less output current ripple, simple in structure and operates with high switching frequency.

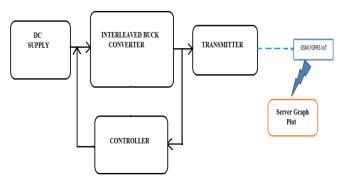

The word 'Interleaving' refers to paralleling which shares the power flow between two or more conversion chain and helps to minimize the input current ripple and increases efficiency on the converter. The block diagram of closed loop of Interleaved buck converter is as shown in the Fig 3. It is mainly consists of following

- DC supply: The function of the DC supply is to provide 12V DC like battery which gives power for the operation of the converter.

- Design and development of Interleaved converter: This converter shares the power flow between two or more conversion chain which helps to minimize the input current ripple and to achieve high efficiency on the converter. It implies a reduction in the size, weight and volume of the inductors and capacitors.

- Due to the simple structure and low control complexity of interleaved buck converter, it is used in applications where non isolation, step down conversion ratio, high output current with low ripple is required[3].

- Design and development of PID Controller: To meet the steady state stability by minimizing the transients in the initial conditions. It avoids the fluctuations and ripple present in the output voltage. The output voltage of this proposed converter is given to the transmitter of GPRS module

- Transmitter chip[ESP8266EX]: The function of the transmitter is to transmits the voltage value from one station to another station

- Receiver of the GPRS IoT module: It receives the variation of the voltage value even in remote station which can be regulated by using the PID controller

- Server Graph Plot: This is the display unit of the voltage value which is received from the transmitter[8].

Fig 3: Block diagram of closed loop of Interleaved buck converter for the Femto cell technology

## 4. DESIGN OF POWER SOURCE CONVERTER

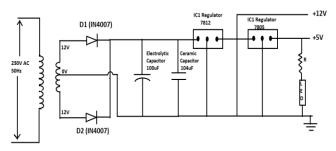

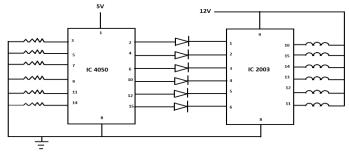

Power Supply unit: The circuit needs two different dual voltages, +5V and +12V, to work which are supplied by this specially designed power supply. The main object of this power supply is to deliver the required amount of stabilized and pure power to the circuit.It mainly consists of the following components namely.

1. Step-down Transformer: The transformer rating is 230V AC at primary winding and 12-0-12V, 1A across secondary winding.

2. Rectifier Stage: The two diodes D1 and D2 are connected across the secondary winding of the transformer as a full-wave rectifier.

3. Filter component :The Capacitor C1 is used for filtering purpose in order to obtain the stable output voltage which is connected across the rectifier output. Ceramic capacitor used to reduce the noise effect and electrolytic capacitor is used to removes the pulsating DC i.e ripples in DC.

4. Voltage Regulation Stage: In this circuit, the three terminal voltage regulated IC7812 and IC7805 IC is used to get regulated D.C. output of +12V and +5V respectively. In the three terminals, pin 1 is input which represent the rectified and filtered D.C. is connected. Pin 2 is common pin which is grounded. The pin 3 gives the stabilized D.C. output to the load. The circuit diagram of the power supply unit is as shown in figure 4.1 (a).

Fig 4.1(a): Circuit diagram of power supply unit

The Buffer, Driver & Driver circuit for the power supply protection of the circuit has been used. Buffers does not affect the logical state of a digital signal and normally used to provide extra current drive at the output but can also be used to regularize the logic present at an interface (i.e. logic 1 input results in a logic 1 output whereas logic 0 input results in a logic 0 output). Drivers are used to drive the relay i.e the output is complement of input which is applied to the drive and current will be amplified.Relays is an electromagnetic device used to drive the load connected across the relay and the output of relay can be connected to controller or load for further processing.

Fig 4.2(b): Circuit diagram of Buffer, Drivers and Relays

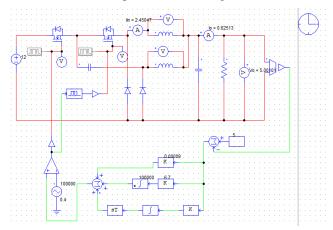

## 5. CIRCUIT DIAGRAM OF INTERLEAVED BUCK CONVERTER FOR FEMTOCELL TECHNOLOGY

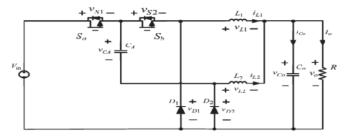

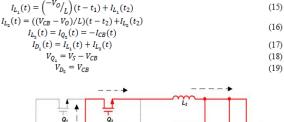

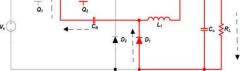

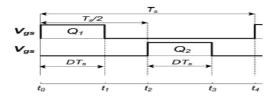

The Interleaved Buck Converter has low switching losses and improved step-down conversion ratio, which is suitable for the applications where the input voltage is high and the operating duty is below 50%. The voltage stress across all the active switches is half of the input voltage before turn-on or after turnoff when the operating duty is below 50%, the capacitive discharging and switching losses can be reduced. The circuit diagram of interleaved buck converter is as shown in the Fig 5.1. It consists of two active switches Q1 & Q2, inductors L1 & L2, diodes D1 & D2, capacitor C, resistor R load and the voltage source Vin.

Fig 5.1: Circuit diagram of the Interleaved buck converter

The capacitor C should be large should be large enough in order to maintain the constant output voltage Vo. All the power semiconductors should be ideal in nature. The two inductors L1 & L2 should be same. Coupling capacitor helps to connects the two circuit which allows AC i.e high frequency and blocks DC i.e low frequency should be large which acts as a voltage source. The circuit diagram of interleaved buck converter consists of 4 modes namely

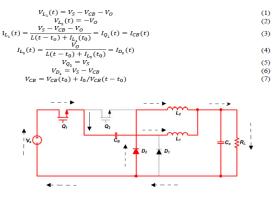

Mode 1 (t0 - t1): Mode 1 begins when Q1 is turned ON & D2 is Forward biased at to. The current iL1(t) flows through Q1, Cb & L1 and voltage of coupling capacitor Vcb is charged. The voltage across inductor L1 is VL1= Vs-Vcb-Vo (+ve value), hence iL1(t) increases linearly and voltage across inductor L2 is VL2= -Vo(-ve value),hence iL2(t) decreases linearly. The voltage across the switch Q2 and diode D1 are Vq2= Vs & Vd1= Vs- Vcb respectively. The circuit diagram of the mode 1 operation is shown in the figure 5.2. The equation obtained during the mode 1 operation is as follows

Fig 5.2: Circuit diagram for Mode 1 operation

• Mode 2 (t1 – t2): The Mode 2 begins when Q1 is turned OFF at t1. The currents iL1(t) and iL2(t)freewheels through D1 and D2 respectively. The voltage across inductor L1 and L2 are VL1(t) =VL2(t) = -Vo (-ve value) hence iL1(t) and II2(t) decreases linearly. The voltage across the switch Q1 and diode Q2 are Vq1(t) = Vs – Vcb and Vq2(t) = Vcb respectively. The circuit diagram of the mode 2 operation is shown in the figure 5.3. he equation obtained during the mode 2 operation is as follows

Fig 5.3: Circuit diagram for Mode 2 operation

## International Journal of Emerging Technologies in Engineering Research (IJETER) Volume 7, Issue 5, May (2019) www.ijeter.everscience.org

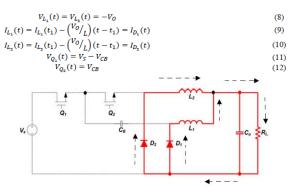

.Mode 3 (t2 - t3): The Mode 3 begins when Q2 is turned ON at t2. The current iL1(t) freewheels through D1 and iL2(t) flows through D1, Cb, Q2 & L2. Thus Vcb is discharged. The voltage across inductor L1 is VL1= -Vo (-ve value), hence iL1(t) decreases linearly. The voltage across inductor L2 is VL2=Vcb-Vo(+ve value),hence iL2(t) increases linearly. The voltage across the switch Q1 and diode D1 are Vq1= Vs - Vcb & Vd1= Vcb respectively. The circuit diagram of the mode 3 operation is shown in the figure 5.4. The equation obtained during the mode 3 operation is as follow

$$V_{L_{2}}(t) = -V_{0}$$

(13)

$V_{L_{3}}(t) = V_{CB} - V_{0}$  (14)

Fig 5.4: Circuit diagram for Mode 3 operation

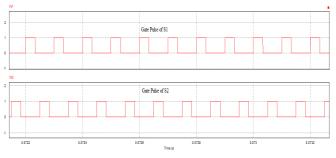

• Mode 4 (t3 – t4): Mode 4 begins when Q2 is turned OFF at t3, and its operation is same as Mode 2. The gate pulses given for the interleaved buck converter is shown in the figure 5.5

Fig 5.5: Gate pulses given for Interleaved Buck Converter

According to the design the inductor value is given by the equation  $L = [(Vs-Vo)/diL^* 2f]^*D$  and L1 = L2 = L/2. The capacitor value is given by the equation  $C = (1-2D)/(8^*L^*(dV/Vo)^*(2^*f)^2)$ . The components value present in the circuit diagram is shown in the table 1

| Table 1: Specification the con | ponents value according to the design |

|--------------------------------|---------------------------------------|

|                                |                                       |

| Sl.no | Name of the parameter | Values |

|-------|-----------------------|--------|

| 1.    | Input Voltage         | 12V    |

| 2.    | Output Voltage        | 5V     |

| 3. | Power Rating        | 10W     |

|----|---------------------|---------|

| 4. | Inductor L1 & L2    | 1.439mH |

| 5. | Capacitor           | 21.71nF |

| 6. | Switching frequency | 100KHz  |

| 7. | Resistance          | 10ohm   |

## 6. SIMULATION & HARDWARE RESULTS OF THE INTERLEAVED BUCK CONVERTER

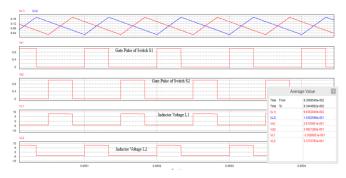

• Open loop simulation

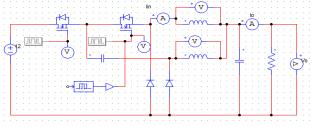

The simulation circuit and result of the interleaved buck converter in open loop is as shown in figure 6.1(a)(b)(c)

Fig 6.1(a): Open Loop Simulation of the interleaved buck converter

Fig 6.1(b): Open Loop Simulation result of output voltage Vo & current Io

Fig 6.1(c): Open Loop Simulation result of Inductor current L1, L2, gate pulse of S1 & S2, inductor voltages of VL1 & VL2

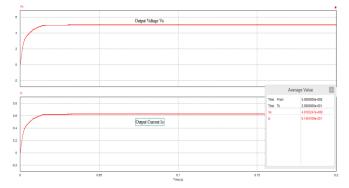

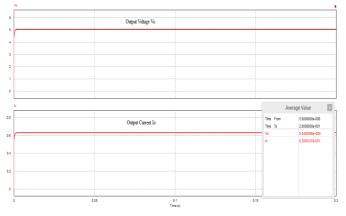

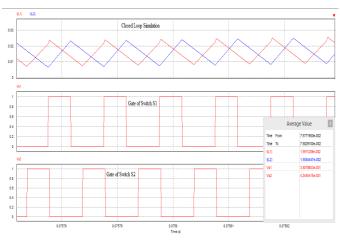

Closed loop simulation

The simulation circuit and result of the interleaved buck converter in closed loop is as shown in figure 6.2(a)(b)(c)

Fig 6.2(a): Closed Loop Simulation of the interleaved buck converter with PID controller

Fig 6.2(b): Open Loop Simulation result of output voltage Vo & current Io

Fig 6.2(c): Closed Loop Simulation result of Vo, VL1 & VL2 voltages of interleaved buck converter

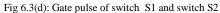

• Hardware implementation of Interleaved buck converter: The power supply unit is connected to the buffer, driver circuit with the interleaved buck converter of the input voltage is 12V and the output voltage of 5V. The closed controller of PID is working with the help of Node MCU chip to obtain the constant output 5V.

Fig 6.4(a): Hardware implementation of the interleaved buck converter with normal and variable supply

Fig 6.4(b): Hardware output result of the interleaved buck converter with input voltage of 12V and output voltage 5V

Fig 6.4(b): Hardware output result of fluctuations of the input voltage with the constant output voltage

#### 7. RESULTS AND DISCUSSION

The overall outcome of the interleaved buck converter for Femto cell is outlined as follows:

Table 2: Open Loop simulation results of Interleaved Buck converter for femtocell technology

| Sl.no | Parameters               | Result values |

|-------|--------------------------|---------------|

| 1     | Input Voltage Vin        | 12V           |

| 2     | Output Voltage Vo        | 5.04V         |

| 3     | Input Current lin        | 0.63          |

| 4     | Output Current Io        | 0.405         |

| 5     | Output voltage ripple    | 3.2%          |

| 6     | Output current ripple    | 0.4%          |

| 7     | Voltage from Inductor L1 | 0.0389V       |

| 8     | Voltage from Inductor L2 | 0.0230V       |

| 9     | Current from Inductor L1 | 0.3832A       |

| 10    | Current from Inductor L2 | 0.25A         |

Table 3: Closed Loop simulation results of Interleaved Buck converter for femtocell technology

| Sl.no | Parameters            | Result values |

|-------|-----------------------|---------------|

| 1     | Input Voltage Vin     | 12V           |

| 2     | Output Voltage Vo     | 5.012V        |

| 3     | Input Current Iin     | 0.62655A      |

| 4     | Output Current Io     | 0.62632A      |

| 5     | Output voltage ripple | 2.5%          |

| 6  | Output current ripple    | 0.2%       |

|----|--------------------------|------------|

| 7  | Voltage from Inductor L1 | 0.01059V   |

| 8  | Voltage from Inductor L2 | 0.0134V    |

| 9  | Current from Inductor L1 | 0.6249A    |

| 10 | Current from Inductor L2 | 0.0000149A |

1. In order to maintain output voltage constant wrt flautation of the input, PID controller has been used.

2. Output voltage and output current ripples are less in closed loop simulation when compared to open loop.

3. The efficiency of this converter for femtocell technology in open loop is 40% but in the closed the efficiency has increased upto 60%.

4. Interleaved refers to parelelling of the two circuits which reduces the input ripples of the voltage and current compared to conventional buck converter.

5. Hardware implementation of IBC results satisfies the software result with the output voltage of 5V.

## 8. CONCLUSION

In this paper, the different types of small cells used for strengthen the network connectivity along with the femtocell technology has been discussed. In order to reduce the input voltage ripple and to increase the efficiency interleaved buck converter is suitable for the supply side of the femtocell. The role of power electronics on the supply side of the femto cells are discussed. In the block diagram of the closed loop of PID controller, the importance of the transmitter and receiver has been analyzed. Hence the comparison of the open loop and the closed operation of the interleaved buck converter has been done with the increasing in the stability along with the dynamic performance by using PID controller has been achieved both in the simulation results and hardware results.

## REFERENCES

- Il-Oun Lee, Shin-Young Cho, and Gun-Woo Moon, "Interleaved Buck [1] Converter Having Low Switching Losses and Improved Step-Down Conversion Ratio", IEEE Transaction on Power Electronics, Vol. 27, No. 8, August 2018.

- [2] Ashwini A. Patil1, D. S. Chavan, "Comparative Analysis of Buck Converter and Modified Interleaved Buck Converter for Standalone Wind Energy System", International Journal of All Research Education and Scientific Methods (IJARESM) ISSN: 2455-6211, Volume 4, Issue 5. May- 2017.

- Y. M. Chen, S. Y. Teseng, C. T. Tsai, and T. F. Wu, "Interleaved buck [3] converters with a single-capacitor turn-off snubber," IEEE Trans. Aerosp. Electronic Syst., vol. 40, no. 3, pp. 954-967, Jul. 2016.

- V. Chandrasekhar, J. G. Andrews and A. Gatherer, "Femtocell networks: A survey," IEEE Comm. Magazine, vol. 46, no. 9, pp. 59–67, [4] Sep. 2008.

- A. Damnjanovic, J. Montojo, Y. Wei, T. Ji, T. Luo, M. Vajapeyam, T. [5] Yoo, O. Song, and D. Malladi, "A survey on 3GPP heterogeneous networks," IEEE Wire. Com.

## International Journal of Emerging Technologies in Engineering Research (IJETER) Volume 7, Issue 5, May (2019) www.ijete

- [6] V. Chandrasekhar, J. G. Andrews, T. Muharemovic, Z. Shen and A.Gatherer, "Power control in two-tier femtocell networks," IEEE Trans. Wireless Commun., vol. 8, no. 8, pp. 4316–4328, Aug. 2009.

- [7] 3GPP TR 25.967 (Release 10), "Universal Mobile Telecommunications System (UMTS); Home Node B (HNB) Radio Frequency," pp. 1–56, 2011, version 10.0.0.

- [8] P. Xia, V. Chandrasekhar, and J. G. Andrews, "Open vs. closed access femtocells in the uplink," IEEE Trans. on Wireless Communications, vol. 9, no. 12, pp. 3798 – 3809, Dec. 2010.

- [9] D. Calin, H. Claussen, and H. Uzunalioglu, "On femto deployment architectures and macrocell offloading benefits in joint macro-femto deployments," IEEE Comm. Mag., vol. 48, no. 1, pp. 26–32, 2010.

- [10] H. A. Mahmoud and 'I. Guvenc", "A comparative study of different deployment modes for femtocell networks," in IEEE 20th Inter. Symp. on Personal, Indoor and Mobile Radio Commun., Tokyo, Japan, pp. 1– 5, Sep. 2009.

Authors

Yashaswini.H.N. was born in Hassan in 17-01-1996. She Received B.E (E&E) degree from VTU University & Perusing M.tech in R.V College of Engineering. Paper has been accepted on the topic of "Performance Analysis Of Load Testing By Using Femtocell Technology for mobile communication" for International Academic Conference on Engineering, Technology and Innovations (IACETI) organized by Academics world on 17th -18th July 2019 at Las Vegas, USA.Certification of paper presentation on the topic of "Design and Analysis of Dual input Flux Additive DC-DC Converter for Hybrid Electric Vehicle" organized by PWSIM solutions for electrification on February 28th at World Trade Center, Bengaluru 2019.She Published paper in National Conference on the Topic of performance Analysis of Quadratic Boost Converter by using Prism tool in 2018. Her area of interest includes Power Electronics applications in drive, Femto cell related to Telecommunications.

**Dr. S. G. Srivani** was born in Bengaluru, in 1963. She Received B.E (E&E).degree from Bangalore University, Bengaluru in 1986, M.E. (power system) degree from Bangalore university, Bengaluru in 1990 and PhD in 2011 from National Inst. of Technology, Karnataka (NITK)– Surathkal, Mangalore, India. Srivani joined RV College of Engineering, Bengaluru, India in 1990 as lecturer and presently working as Associate professor in the department of Electrical and Electronics

Engineering. She is a fello of Institute of Engineers (FIE), life member of Indian Society for Technical Education [ISTE] and senior member of IEEE. She has published more than 70 technical research papers in various National and International Journals and conferences. Her areas of interest include power system protection, signal processing, power quality, Renewable energy sources, Grid integration, smart grid, Power electronics applications industrial drives and energy harvesting, Fuzzy logic and ANN Applications to power system.